WP 4 - System-level explorations

Presentation

WP4 deals with high level of integrated circuit design. Specific high level simulation framework environment will be developed as well as metrics.

Objectives

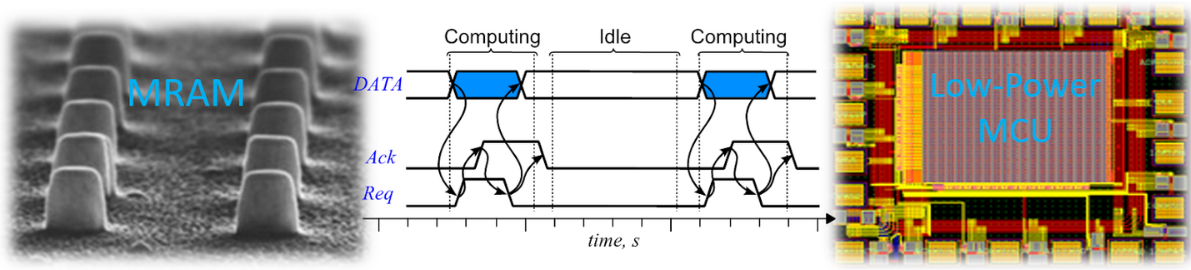

- Study how to exploit the MRAM technologies to improve energy efficiency, with system-level explorations (sizing, hierarchy, hybridization)

- Evaluate at the system-level the gains provided by peSTT, SOT compared to standard technologies..

- Evaluate at the system-level the gains provided by the innovative IPs compared to a standard IPs.

Description of work

System level specifications

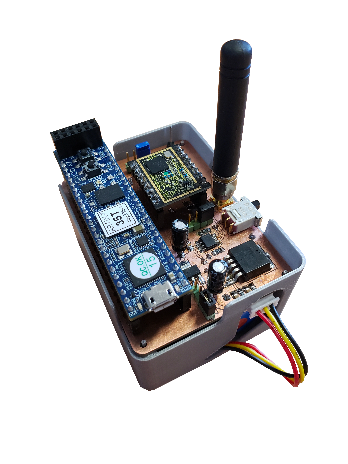

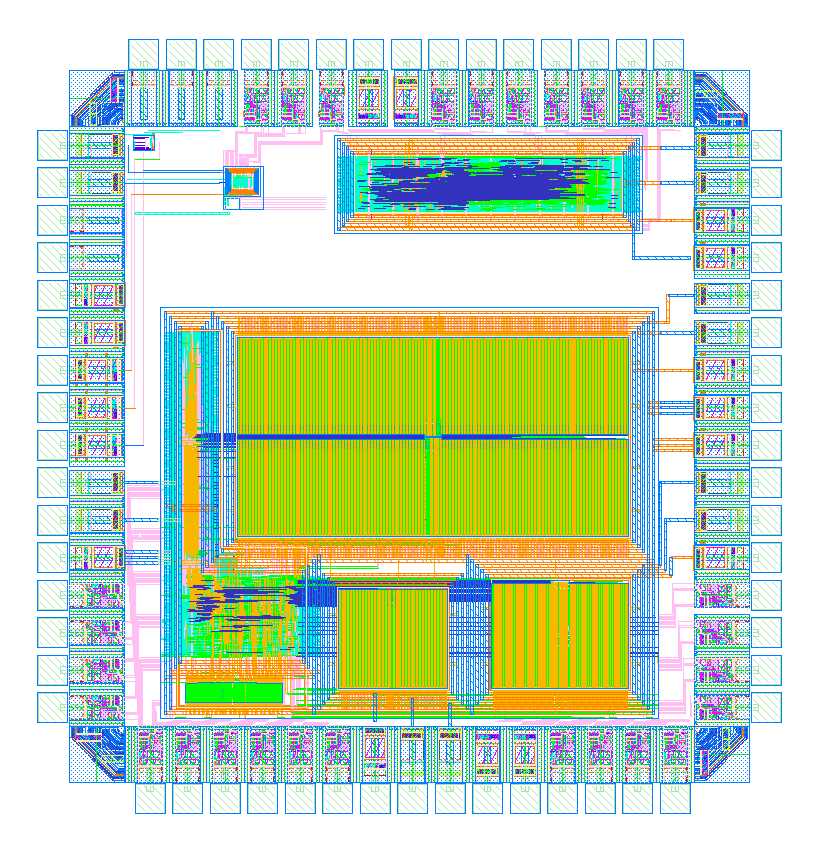

We will define at the system-level a generic architecture able to demonstrate the value of synergy between NV storage and asynchronous design methodology. Based on related works on ultra-low-power MCUs, the requirements for both processors and memories will be defined according to the targeted application scenarios. LIRMM will propose scenarios, with other partner experience, to cover the huge range of IoT applications. Several kinds of applications will be addressed. Nevertheless, these statements allow determining target scenarios to properly compare usual solution with our proposed solution. An important aspect of this study will be a characterization of energy sources and analysis of performance requirements and power budgets for the chosen scenarios.

Exploration tool development

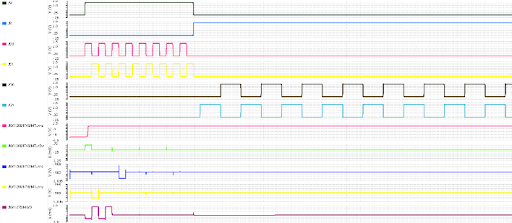

LIRMM will setup an exploration framework that will be used to simulate, evaluate and compare at system level. The main objective is to have a reference, based on the scenario issues and metrics serving as benchmarking. In this way it will be possible to guarantee that a fair comparison could be done. We will use an architecture simulator and high-level memory models, to make a set of evaluations on real applications. This performance evaluation tool will be based on a dedicated flow to adapt to this project. Application evaluations will be directly extracted from the system-level simulations, with the ability to choose the target. This flow relying on simulation and emulation will be adapted depending on the chosen architecture and the sizing IPs.

Design space exploration and simulations

Given the application benchmarks and the set of metrics different configurations of the system will be simulated with the tool developed. In this way, it will be possible to compare, for a given system configuration, an architecture based on standard architectures , to innovative architectures we propose. These simulations will allow fair comparisons and performance/energy gains evaluations, expected in the range of 1 order of magnitude. Furthermore, the results will be compared to current industrial solutions with the standard benchmarking methodology.