WP 2 - Modeling and standard cells

Presentation

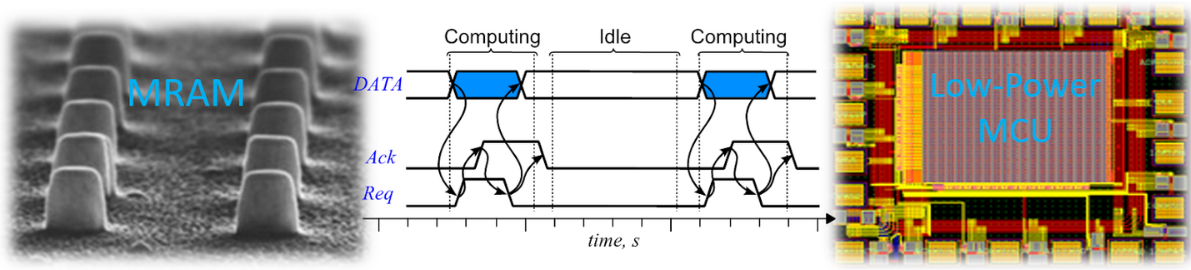

WP2 aims at providing magnetic tunnel junction simulation model for full custom design, including both non-volatile logic and memories. CAD tool environment will be developed.

Objectives

- Provides all necessary tools and environment to develop innovative IPs, including MTJs compact model.

- Conceive and design innovative non-volatile IPs.

Description of work

MTJ compact model

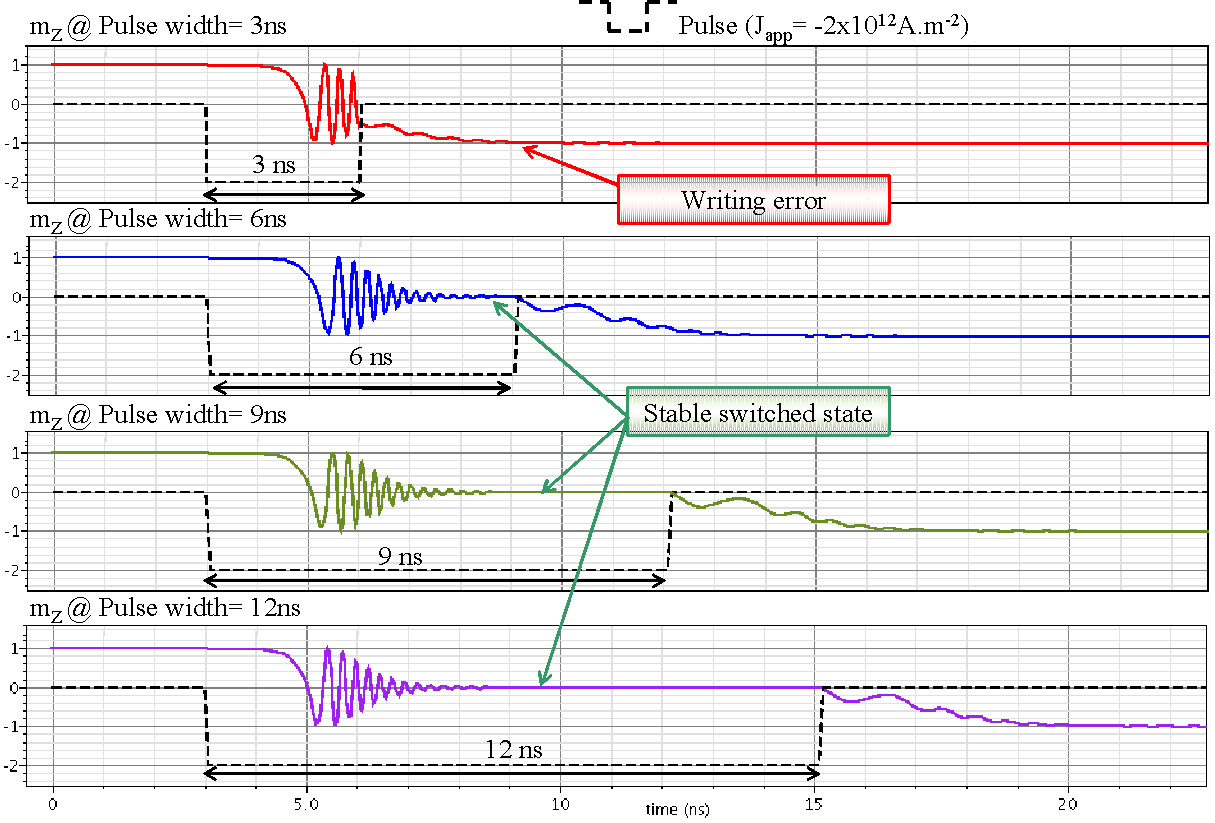

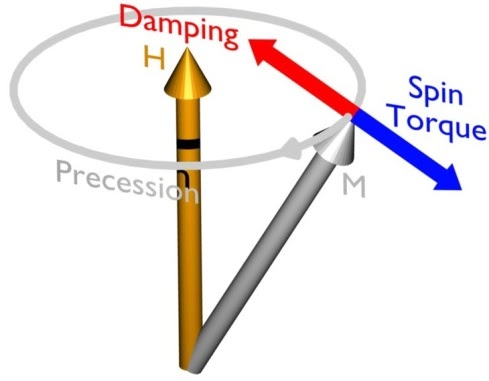

In order to design full custom non-volatile cells, it is mandatory to have device compact models to run electrical simulations. Since we intend to explore both peSTT and SOT based innovative cells, both compact models are necessary. This work will be based on the huge experience of Spintec in modeling and MRAM physics.SOT-MRAM behavioural model need to be developed for the design of all SOT-based IPs.

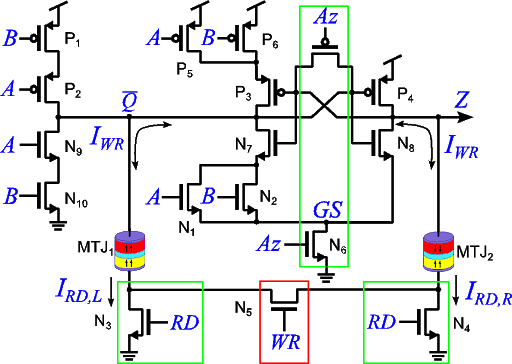

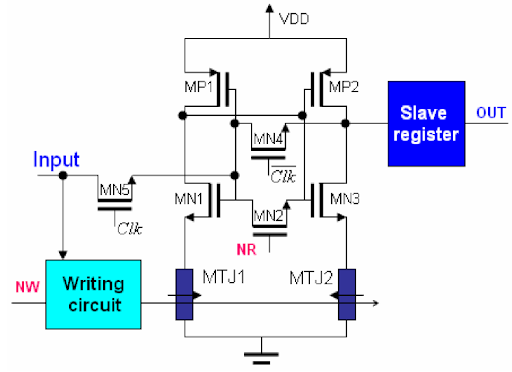

Standard cell design and characterization

We will develop innovative standard cells. The strong experience of Spintec in non-volatile cell design marked by several patents will be a key aspect. Innovative peSTT and SOT based non- volatile cell will be proposed with the only objective to be extremely energy efficient, when writing and reading the MTJ but in standby mode particularly. The FDSOI features will be fully explored.

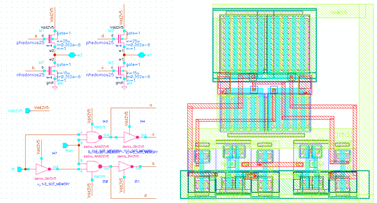

Library development and characterization

All these IPs developed will be accurately simulated and characterized, using several corners, Provided files are .lib for the logic synthesis, Verilog behavioural models for digital simulation of the complete processors and .lef from cell layouts for the automatic place and route layout.